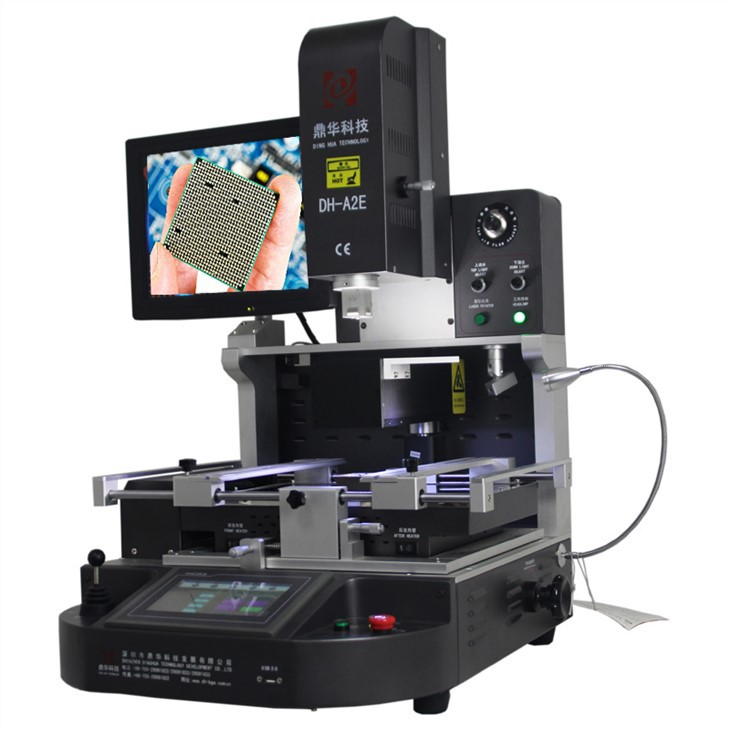

Автоматична оптична паяльна станція BGA

Широко використовується для ремонту на рівні чіпа для материнської плати мобільного телефону, ноутбука, комп’ютера, телевізора, кондиціонера тощо. Він має високий рівень успішного ремонту та високий ступінь автоматизації та заощаджує багато людських зусиль. Ми є професійним виробником цієї машини і маємо ці машини в наявності.

Опис

Автоматична оптична паяльна станція BGA

1. Застосування автоматичної оптичної паяльної станції BGA

Материнська плата комп'ютера, смартфона, ноутбука, логічної плати MacBook, цифрової камери, кондиціонера, телевізора та іншої електроніки

обладнання з медичної промисловості, галузі зв'язку, автомобільної промисловості тощо.

Підходить для різних видів чіпів: BGA, PGA, POP, BQFP, QFN, SOT223, PLCC, TQFP, TDFN, TSOP, PBGA, CPGA, світлодіодний чіп.

2. Характеристики продукту Auto Optical BGA Rework Station

• Високий рівень успішного ремонту на рівні сколів. Процес розпаювання, монтажу та пайки відбувається автоматично.

• Точне вирівнювання кожного паяного з'єднання можна гарантувати за допомогою камери CCD з оптичним вирівнюванням.

• Точний контроль температури можна забезпечити за допомогою 3 незалежних зон нагріву. Машина може встановити і зберегти

1 млн температурного профілю.

• Вбудований вакуум у монтажній головці автоматично захоплює мікросхему BGA після завершення розпаювання.

3. Специфікація автоматичної оптичної паяльної станції BGA

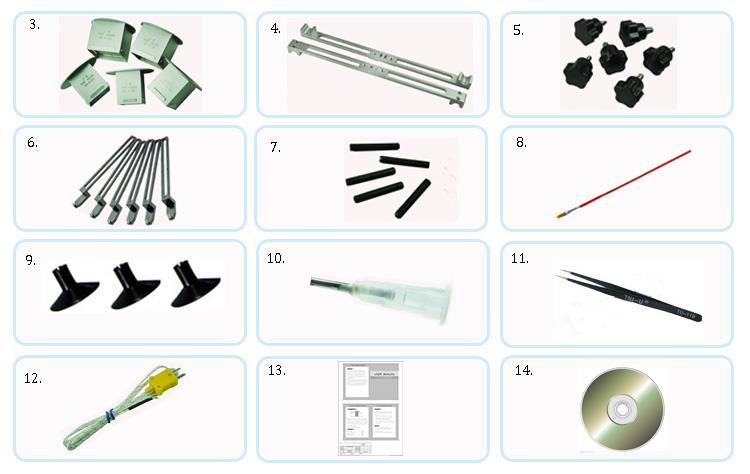

4. Деталі автоматичної оптичної паяльної станції BGA

CCD-камера (система точного оптичного вирівнювання); 2.HD цифровий дисплей; 3. Мікрометр (відрегулюйте кут стружки);

4.3 незалежні обігрівачі ( гаряче повітря та інфрачервоні ) ; 5. Лазерне позиціонування ; 6. Інтерфейс сенсорного екрану HD, керування ПЛК;

7. світлодіодні фари; 8.Керування джойстиком.

5. Чому варто вибрати нашу автоматичну оптичну паяльну станцію BGA?

6.Сертифікат автоматичної оптичної паяльної станції BGA

7. Упаковка та відвантаження автоматичної оптичної паяльної станції BGA

8.FAQ

Як перевірити чіп?

Початковий тест чіпа на системному рівні

SoC базується на глибоких субмікронних процесах, тому тестування нових пристроїв на Soc вимагає абсолютно нового підходу. Оскільки кожен функціональний компонент

має власні вимоги до тестування, інженер-конструктор повинен скласти план тестування на початку процесу проектування.

Має бути реалізований поблочний план тестування для пристроїв SoC: правильно налаштовані засоби ATPG для тестування логіки; короткий час тестування; новий швидкісний

моделі несправностей і кілька тестів пам'яті або невеликих масивів. Для виробничої лінії метод діагностики не тільки знаходить несправність, але й відокремлює її

несправний вузол від робочого вузла. Крім того, слід використовувати методи тестового мультиплексування, коли це можливо, щоб заощадити час тестування. У сфері високо

інтегроване тестування IC, тестовані методи проектування ATPG і IDDQ мають потужний механізм відокремлення несправностей.

Інші фактичні параметри, які необхідно планувати заздалегідь, включають кількість контактів, які потрібно сканувати, і обсяг пам’яті на кожному кінці контакту.

Граничні сканування можуть бути вбудовані в SoC, але не обмежуються тестами з’єднань на платах або модулях з кількома кристалами.

Незважаючи на те, що розмір мікросхеми зменшується, мікросхема все ще може вміщувати від мільйонів до 100 мільйонів транзисторів, а кількість тестових режимів зросла до безпрецедентної

рівнів, що призводить до більш тривалих циклів тестування. Цю проблему можна перевірити. Режим стиснення для вирішення, ступінь стиснення може досягати від 20 до 60 відсотків. Для сьогодення масштабно

дизайн мікросхеми, щоб уникнути проблем з ємністю, необхідно знайти тестове програмне забезпечення, яке може працювати на 64-розрядних операційних системах.

Крім того, тестове програмне забезпечення стикається з новими проблемами тестування, спричиненими глибокими субмікронними процесами та збільшенням частоти. У минулому тестовий режим ATPG для

тестування статичних несправностей блокування більше не використовувалося. Додавання функціональних шаблонів до традиційних інструментів ускладнювало пошук нових недоліків. Кращий підхід - це

класифікувати минулі групи функціональних режимів, щоб визначити, які несправності неможливо виявити, а потім створити режим ATPG, щоб зафіксувати ці відсутні типи несправностей.

Оскільки проектна потужність збільшується, а час тестування на транзистор зменшується, для виявлення проблем, пов’язаних зі швидкістю, і перевірки синхронізації схеми, синхронний метод тестування

повинні бути працевлаштовані. Синхронне тестування має включати кілька моделей несправностей, включаючи моделі перехідних процесів, затримки шляху та IDDQ.

Деякі компанії в галузі вважають, що найефективнішою стратегією тестування може бути поєднання блокувальних, функціональних і перехідних процесів/затримки шляху. Для глибокого

субмікронні чіпи та робота на високій частоті, тестування перехідних процесів і затримки шляху є навіть більш важливим.

Для вирішення проблеми точності ATE при синхронізації тестового ядра та здешевлення необхідно знайти новий метод, що спрощує інтерфейс

тестовий пристрій (перевірка перехідних процесів і затримки шляху потребує точного тактового сигналу на інтерфейсі тестового пристрою), це гарантує, що сигнал є достатньо точним під час тесту.

Оскільки існує висока ймовірність виробничих дефектів у блоці пам’яті SoC, BIST пам’яті повинен мати функцію діагностики. Як тільки проблема знайдена,

несправний блок адреси може бути відображено в резервній пам’яті резервного блоку адреси, а виявлена адреса помилки буде відкинута. Уникайте викидання

весь дорогий чіп.

Тестування невеликих блоків вбудованої пам'яті усуває потребу в додаткових вентилях або логіці керування. Наприклад, методи тестування векторного перетворення можуть конвертувати

функціональні режими в ряд режимів сканування.

На відміну від методу BIST, функціональний вхід обхідного блоку пам'яті не потребує додаткової логіки. Оскільки не потрібна додаткова тестова логіка, SoC

інженери-розробники можуть повторно використовувати тестові шаблони, які були сформовані в минулому.

Розширені інструменти ATPG не тільки тестують макроси паралельно, але й визначають наявність конфліктів, а також детально описують, які макроси можна тестувати паралельно, а які

макроси не можна тестувати паралельно. Крім того, ці макроси можна ефективно перевірити, навіть якщо годинник макросу збігається з годинником сканування (наприклад, синхронна пам’ять).

В даний час тестових точок на щільній двосторонній платі недостатньо, і кожен складний чіп повинен бути оснащений схемою граничного сканування. без

граничне сканування, пошук виробничих дефектів на рівні плати досить складно, і їх навіть неможливо знайти. За допомогою граничного сканування тестування на рівні плати надзвичайно просте

і незалежно від логічної схеми мікросхеми. Граничне сканування також може налаштувати режим ATPG для ланцюга сканування мікросхеми на будь-якому етапі виробництва.